# Схемотехника КМОП полных сумматоров

# В. В. Шубин

В работе описаны принципы построения схемотехники ячейки полного КМОП сумматора. Приведены наиболее распространённые конструктивные решения различных стилей проектирования, описаны их достоинства и недостатки. Представлены результаты моделирования и сравнения описанных решений. Кроме того, предложено решение ячейки сумматора, которое обладает превосходящими характеристиками по быстродействию по формированию сигнала переноса в сравнении с известными сумматорами и, следовательно, позволяет добиться более высокого быстродействия при построении многоразрядных сумматоров.

Ключевые слова: сумматор, схемотехника, КМОП, проектирование.

## 1. Введение

Сумматор является одним из блоков цифровой схемотехники, который наиболее часто используется при построении современных цифровых СБИС. Широкое применение сумматоров объясняется следующими причинами:

- сложение двоичных данных является основной операцией формирования основных логических функций вычислительных систем, таких как суммирование, вычитание, умножение, деление, возведение в степень и т.д. [1–4];

- многоразрядный сумматор является одним из важнейших решающих блоков для достижения предельных требований по быстродействию цифровых сигнальных процессоров (ЦП, DSP) и узлов центральных процессоров (ЦПУ, CPU) [5];

- сумматор является основным блоком для построения арифметико-логических устройств (АЛУ, ALU) [5, 6];

- ячейка одноразрядного сумматора является важной составляющей схем финальной обработки сигналов некоторых современных архитектур быстродействующих аналогоцифровых преобразователей (АЦП, ADC).

В связи с этим в последние годы разработчики современных СБИС уделяют повышенное внимание вопросу исследования новых архитектурных, схемотехнических, топологических решений, стилей, методологий проектирования сумматоров для достижения более высоких характеристик по быстродействию и потребляемой мощности [4, 7–10].

В данной работе рассматриваются сумматоры, которые принято относить к классу параллельных сумматоров с последовательным (сквозным) переносом (ripple carry full adder) [11], выполненных по КМОП (комплементарные металл-оксид-полупроводник структуры) технологии. В работе представлена новая схема ячейки одноразрядного КМОП сумматора, позволяющая добиться наилучших показателей по быстродействию, а также приводятся данные сравнения с некоторыми наиболее распространёнными ячейками полных сумматоров.

Статья построена следующим образом: в разделе 2 кратко описаны основные критерии оценки технических характеристик сумматоров, в разделе 3 приведены некоторые распространённые схемотехнические решения ячеек КМОП полных сумматоров, в разделе 4 представлено новое схемотехническое решение одноразрядного полного КМОП сумматора, обладающего превосходящими характеристиками по быстродействию, в разделе 5 приведены

результаты моделирования и сравнения ранее описанных известных сумматоров и нового схемотехнического решения.

## 2. Критерии оценки характеристик сумматоров

Основными критериями оценки характеристик сумматоров являются быстродействие и величина потребляемой мощности [12].

Кроме того, часто при сравнении различных конструктивных решений сумматоров используется совокупный показатель, который одновременно характеризует и потребляемую мощность, и задержку распространения сигналов (Power-Delay Product, PDP). Однако сам по себе этот показатель мало информативен и в основном применяется только в случаях, когда при сравнении различных конструкций основные критерии заметно расходятся по своему значению.

Рассмотрим более подробно основные критерии сравнения сумматоров [3, 11–14].

#### 2.1. Быстродействие

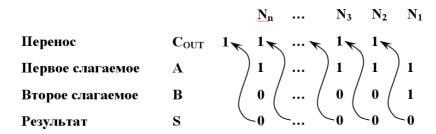

На рис. 1 представлена схема формирования переноса в каждом разряде.

Рис. 1. Схема формирования переноса в каждом разряде

Эта схема показывает, что в параллельных сумматорах с последовательным переносом общее быстродействие (максимальное время сложения) определяется количеством разрядов и временем задержки формирования и распространения сигнала от входа переноса  $C_{\text{IN}}$  до выхода переноса  $C_{\text{OUT}}$  [15]:

$$T_{SUM} = n \cdot T_n \tag{1}$$

здесь n — количество используемых разрядов,  $T_n$  — время формирования и распространения сигнала переноса между двумя соседними разрядами сумматора.

Анализ данной формулы показывает, что существует наихудший случай комбинаций сложения операндов A и B, когда в каждом разряде сумматора, начиная с самого первого (младшего), происходит формирование сигнала переноса  $C_{OUT}$  вплоть до последнего (старшего).

Необходимо заметить, что приведённая формула (1) не учитывает время задержки сложения сигнала переноса  $C_{IN}$ , формируемого в последнем (старшем) разряде с результатом сложения его операндов A и B, т.к. в многоразрядных сумматорах это время составляет небольшую часть общей задержки (уже для восьмиразрядных менее 10%), его редко учитывают. Однако при необходимости более точных расчётов его обязательно следует учитывать:

$$T_{SUM} = n \cdot T_n + T_{Sn} \tag{2}$$

здесь  $T_{Sn}$  — время задержки сложения сигнала переноса  $C_{IN}$ , формируемого в старшем разряде с результатом сложения его операндов A и B.

## 2.2. Потребляемая мощность

Ещё одним важным критерием оценки сумматоров является потребляемая мощность. В общем виде формула общей потребляемой мощности ( $P_{total}$ ) в статических цифровых КМОП схемах приведена ниже [16]:

$$P_{total} = P_{dvnamic} + P_{leakage} + P_{short-circuit} + P_{DC}, \tag{3}$$

здесь  $P_{dynamic}$  — мощность потребления при переключении узлов во время перезаряда узловых ёмкостей, или динамическая мощность,  $P_{leakage}$  — мощность потребления схемы за счёт утечек вследствие неидеальности работы МОП транзистора в режиме отсечки,  $P_{short\text{-}circuit}$  — мощность потребления короткозамкнутого вентиля,  $P_{DC}$  — составляющая потребляемой мощности при использовании в схеме сигналов неполного уровня напряжения относительно разности потенциалов источника питания.

Динамическая мощность потребления в КМОП ИС определяется частотой переключения  $f_s$ , величиной нагрузочной ёмкости узлов  $C_L$ , напряжением источника питания  $V_{DD}$  и величиной размаха напряжения переключения  $V_{swing}$  [16]:

$$P_{dynamic} = f_s C_L V_{DD} V_{swing}, \tag{4}$$

здесь  $f_s$  — тактовая частота,  $C_L$  — узловая ёмкость нагрузки,  $V_{DD}$  — напряжение источника питания,  $V_{swing}$  — амплитуда выходного сигнала на нагрузочной ёмкости  $C_L$ .

Так как в стандартных КМОП схемах  $V_{swing} = V_{DD}$ , то:

$$P_{dynamic} = f_s C_L V_{DD}^2. (5)$$

Кроме того, в классических КМОП схемах значения  $P_{leakage}$  и  $P_{DC}$  пренебрежимо малы и в основном зависят от качества процесса [1–4], ими можно пренебречь. В этом случае:

$$P_{total} = P_{dynamic} + P_{short-circuit}. (6)$$

#### 2.3. Показатель PDP (произведение потребляемой мощности на задержку)

Ещё одним важным критерием сравнения сумматоров является совокупный показатель PDP (Power-Delay Product), который определяется произведением значений потребляемой мощности  $P_{total}$  на задержку распространения сигнала  $T_{delay}$  [11, 12].

$$PDP = P_{total} \cdot T_{delay}. \tag{7}$$

Этот показатель оказывается особенно полезным при анализе возможности применения в специальных приложениях среди конструкций, сравнимых по двум первым показателям (см. разд. 2.1, 2.2).

Существует ещё ряд дополнительных показателей, которые применяются, если значения основных критериев мало различаются и/или цель проекта сформулирована неопределённо [4–6, 12, 13]:

- количество используемых транзисторов;

- нагрузочная способность входных и выходных сигналов;

- размах амплитуды выходных сигналов;

- площадь топологии на кристалле;

- простота реализации топологии.

Эти показатели чаще всего используются при сравнении конструкций сумматоров, выполненных в других стилях проектирования, таких как, например, «мостовой», «на проходных транзисторах», «на передаточных вентилях», «псевдо-nMOS».

## 3. Ретроспектива известных КМОП сумматоров

Рассмотрим несколько наиболее удачных схемотехнических решений ячеек полных КМОП сумматоров с точки зрения достижения наилучших характеристик по основным критериям сравнения, приведённым ранее.

### 3.1. Традиционный КМОП полный сумматор

Среди известных схемотехнических решений сумматоров чаще всего используется т.н. «традиционный КМОП полный сумматор» (Conventional CMOS Full Adder, далее – ТКПС) [3, 4]. Этот сумматор относится к классу зеркальной (иногда называемой дуальной) статической КМОП логики, который характеризуется тем, что его запитывающая часть схемы (Pull-Up Network), выполненная на транзисторах Р-типа, и схема стекания (Pull-Down Network), выполненная на транзисторах N-типа, имеют зеркальную структуру относительно выхода, а каждый Р-канальный транзистор соединён по затвору с соответствующим N-канальным транзистором в комплементарную пару.

Широкое применение этой схемы объясняется рядом её достоинств:

- Физическая реализация данной схемы укладывается в рамки стандартного КМОП технологического процесса и не требует дополнительных операций, усложняющих и увеличивающих затраты на процесс изготовления.

- Полная симметрия схемотехники ТКРС упрощает процесс топологического проектирования и последующую оптимизацию топологии.

- Применение схемотехники ТКРС позволяет достигнуть наилучших показателей по мощности потребления в статическом режиме до близкой к нулю.

- Упрощается оптимизация схемы на схемотехническом уровне (подбор размеров транзисторов) в рамках различных технологических процессов.

Недостатком данной конструкции является повышенное количество используемых транзисторов.

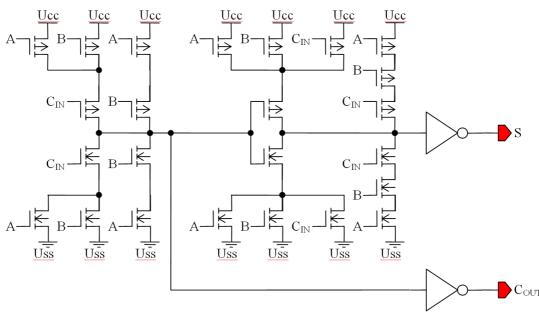

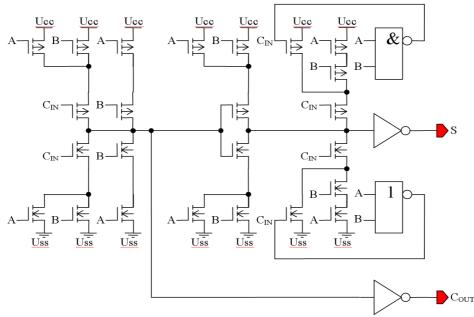

На рис. 2 приведена принципиальная электрическая схема ТКРС на КМОП транзисторах [3, 4].

Рис. 2. Принципиальная электрическая схема ячейки традиционного полного сумматора на КМОП транзисторах (ТКРС)

#### 3.2. Усовершенствованный традиционный КМОП полный сумматор

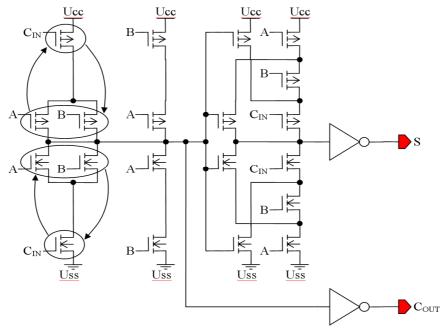

На рис. 3 приводится модификация принципиальной электрической схемы ТКРС на КМОП транзисторах, минимизированная по количеству используемых транзисторов (далее – МТКРС), основанная на такой же зеркальной КМОП логике [17].

Рис. 3. Принципиальная электрическая схема минимизированной ячейки традиционного полного сумматора на КМОП транзисторах (МТКРС)

Преимущества МТКРС над ТКРС следующие:

- МТКРС содержит на четыре транзистора меньше по сравнению с ТКРС.

- МТКРС потенциально обладает более высоким быстродействием по сравнению с ТКРС из-за меньшего количества элементов и связей и, следовательно, имеет меньшее количество паразитных резистивно-ёмкостных элементов.

- МТКРС обладает более высокой надёжностью, так как содержит меньшее количество элементов и, следовательно, связей, соединяющих их.

Недостатком МТКРС является положение транзисторов  $C_{IN}$ , A-B в последовательной цепи схемы переноса, который легко устраняется изменением их расположения относительно источника питания и выходного инвертора, как показано на рис. 3.

#### 3.3. Схемотехника КМОП полных сумматоров на передаточных вентилях

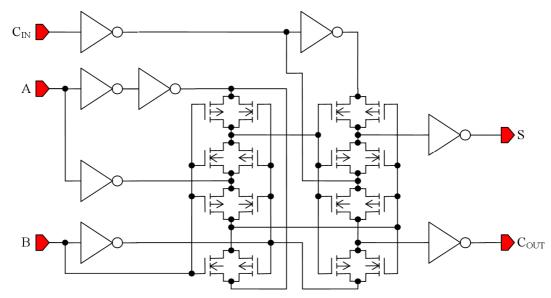

На рис. 4 представлена электрическая принципиальная схема полного сумматора из состава библиотеки стандартных элементов КМОП технологического процесса 0.18 μm предприятия Silterra Malaysia Sdn. Bnd. (Малайзия). Приведённая схема сумматора представляет стиль проектирования логики на «передаточных вентилях» (Full Adder Based on the Transmission Gate Logic) [3, 18].

Рис. 4. Принципиальная электрическая схема ячейки полного сумматора на КМОП транзисторах с использованием передаточных вентилей

КМОП полный сумматор, построенный на передаточных вентилях (далее – СПВ), по сравнению с ТКРС обладает следующими преимуществами:

- СПВ может быть выполнен на меньшем количестве транзисторов. Большее количество транзисторов (30 против 28) использовано в представленной схеме в связи с оптимизацией схемы для достижения максимального быстродействия, и при необходимости от дополнительных инверторов на входах  $C_{IN}$  и A можно отказаться. В этом случае схема может быть реализована на 24 транзисторах;

- СПВ при определённых условиях может обладать более высоким быстродействием вследствие меньшего количества переключаемых вентилей на пути прохождения сигналов от входа до выхода и прежде всего сигнала  $C_{IN}$ , определяющего общее быстродействие многоразрядных сумматоров.

К недостаткам СПВ относятся:

- Высокая мощность потребления вследствие невозможности одновременного формирования прямого и инверсного сигналов для управления передаточными вентилями;

- Сложность проектирования топологии из-за наличия перекрёстных связей в комплементарных транзисторах передаточных вентилей.

# 4. Новое решение построения ячейки одноразрядного полного сумматора

На рис. 5 приведена принципиальная электрическая схема предлагаемой ячейки полного сумматора на КМОП транзисторах (далее – ПРПС) [19].

Рис. 5. Электрическая принципиальная схема новой ячейки полного сумматора на КМОП транзисторах (ПРПС)

Новое решение построения принципиальной электрической схемы ячейки одноразрядного полного КМОП сумматора основано на принципе её работы в составе многоразрядных сумматоров с последовательным переносом и направлено на повышение общего быстродействия.

Быстродействие многоразрядных сумматоров с последовательным переносом определяется задержкой формирования и распространения сигнала переноса от входа  $C_{\rm IN}$  до выхода  $C_{\rm OUT}$  в ячейке одноразрядного сумматора, см. (2). Распространение сигнала переноса зависит от количества переключаемых комплексных вентилей на пути прохождения сигнала от входа  $C_{\rm IN}$  до выхода  $C_{\rm OUT}$  [20], а его формирование в каждом из переключаемых вентилей (при равных условиях: ширины W и длины L каналов всех транзисторов равны) зависит от величин паразитных ёмкостей в каждом узле цепи прохождения сигнала и сопротивлений цепочек последовательно включённых транзисторов между выходными узлами каждого вентиля и шинами источника питания [21].

В табл. 1 приведены количественные значения числа переключаемых вентилей и подключенных к их узлам паразитных элементов.

Таблица 1. Количественные значения числа переключаемых вентилей и подключенных к их узлам паразитных элементов сравниваемых ячеек сумматоров

|                                                                                                  | Схема<br>переноса |       |      | Схема<br>сложения |       |      |

|--------------------------------------------------------------------------------------------------|-------------------|-------|------|-------------------|-------|------|

| Тип сумматора                                                                                    | TKPC              | MTKPC | ПРПС | TKPC              | MTKPC | ПРПС |

| Количество переключаемых вентилей                                                                | 2                 | 2     | 2    | 3                 | 3     | 3    |

| Коэффициент разветвления по входу                                                                | 3                 | 2     | 2    | 4                 | 3     | 6    |

| Коэффициент разветвления по выходу первого вентиля                                               | 2                 | 3     | 2    | 2                 | 3     | 2    |

| Коэффициент разветвления по выходу второго вентиля                                               | _                 | _     | _    | 1                 | 1     | 1    |

| Количество последовательно включённых транзисторов Р-типа/N-типа в первом переключаемом вентиле  | 2/2               | 2/2   | 2/2  | 2/2               | 2/2   | 2/2  |

| Количество последовательно включённых транзисторов Р-типа/N-типа во втором переключаемом вентиле | _                 | _     | _    | 3/3               | 3/3   | 3/3  |

Приведённые в табл. 1 данные позволяют сделать предварительное заключение о возможном рейтинге сравниваемых схем по быстродействию.

Анализ сумматоров, приведённых в разд. 3, 4, и данных табл. 1 показывает, что в сравниваемых сумматорах на обоих выходах S и  $C_{OUT}$  стоят инверторы, а количества переключаемых вентилей равны.

ПРПС по косвенным признакам, определяющим быстродействие многоразрядных сумматоров (формирование и распространение сигнала переноса  $C_{\rm IN}$ ), превосходит сравниваемые по нагрузочной способности внутренних узлов. Данное заключение в дальнейшем подтверждается результатами моделирования.

Сравнение сумматора СПВ по косвенным признакам предложенной схемы затруднено применением в нём передаточных вентилей, однако результаты моделирования его динамических параметров и сравнения с другими сумматорами будут приведены в следующем разделе.

Следует заметить, что в ПРПС увеличена нагрузочная ёмкость для входов сложения операндов A и B, что должно привести к увеличению задержки  $T_{Sn}$  операции сложения.

# 5. Результаты моделирования

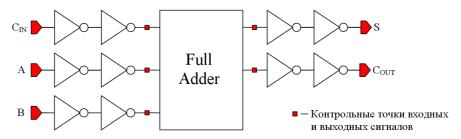

Структурная схема моделирования [22, 23] основана на моделировании переходных процессов в схеме, приведённой на рис. 6, и применении взвешенного, минимизированного, исчерпывающего теста, определяющего время задержки для наихудшего случая формирования сигналов S и  $C_{OUT}$  исследуемой ячейки сумматора.

Рис. 6. Структурная схема моделирования для определения задержек сигналов S и C<sub>OUT</sub> ячейки одноразрядного сумматора

В схеме входные сигналы подаются, а выходные – снимаются через цепочки двух последовательно включённых инверторов, наличие которых приближают условия работы ячейки сумматора к реальным, где, как правило, присутствуют разгоночные и разгоняющие буферные каскады. Также причиной использования этих цепочек является то, что при моделировании применяются входные воздействия, далёкие от реальных сигналов (это либо прямая линия, либо кусочно-ломанная кривая). Использование этих буферизирующих цепочек и контроль задержек на входах и выходах ячейки сумматора позволяет получить данные, максимально приближенные к реальным условиям.

Исходные данные, начальные условия и входные воздействия для моделирования:

- Длины каналов (L) транзисторов Р-типа и N-типа для всех схем равны минимально допустимым размерам выбранного технологического процесса;

- Ширины каналов (W) транзисторов N-типа для всех схем равны минимально допустимым размерам выбранного технологического процесса;

- Ширины каналов (W) транзисторов Р-типа для всех схем равны между собой и определены по принципу оптимальности передаточной характеристики КМОП инвертора [24];

- Реализуется комбинация операндов слагаемых A и B наихудшего случая, когда при поступлении сигнала переноса на вход  $C_{\rm IN}$  на выходе переноса  $C_{\rm OUT}$  формируется сигнал пере-

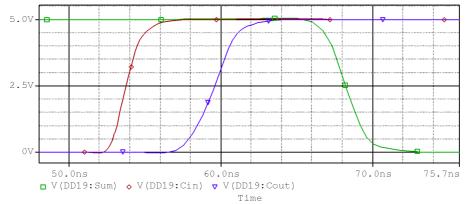

носа в следующий разряд, а на выходе результата сложения S происходит контролируемое изменение: A = 1, B = 0,  $C_{IN} = 0 \rightarrow 1$ . В данном случае происходит изменение сигнала результата сложения  $S = 1 \rightarrow 0$ , как показано на рис. 7.

Рис. 7. Результаты моделирования сумматора, полученные при напряжении питания Ucc = 5 V по схеме, описанной выше

Результаты моделирования получены с помощью программы отображения и обработки результатов Probe, встроенной в систему OrCAD 9.2 ф. Cadence [25], с использованием математической модели 3-го уровня и данными 3-х мкм CMOS технологического процесса.

В табл. 2 приведены результаты моделирования ранее перечисленных ячеек сумматоров по описанной схеме.

| Полный<br>сумматор |       | ржка<br>1S) | Мощность<br>(mW)  | PDP<br>(mW×nS) |        | Кол-во       |

|--------------------|-------|-------------|-------------------|----------------|--------|--------------|

| $(U_{CC} = 5V)$    | Cout  | S           | $f_{cp} = 50 MHz$ | Cout           | S      | транзисторов |

| ТКРС               | 6.023 | 13.674      | 0.665             | 4.005          | 9.093  | 28           |

| MTKPC              | 6.395 | 20.398      | 0.646             | 4.131          | 13.177 | 24           |

| СПВ                | 7.371 | 11.631      | 1.429             | 10.533         | 16.621 | 32           |

| ПРПС               | 5.847 | 14.504      | 0.738             | 4.315          | 10.703 | 36           |

Таблица 2. Результаты моделирования ранее перечисленных ячеек сумматоров

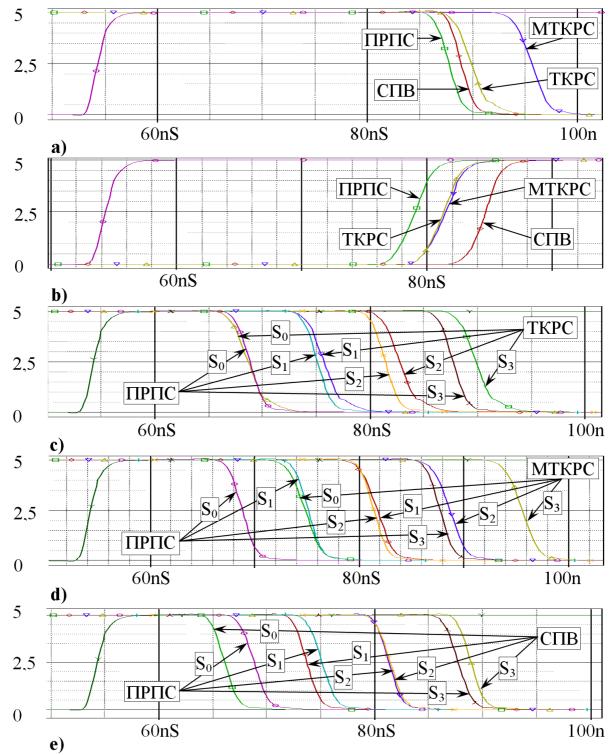

Данные табл. 2 предоставляют разработчику исчерпывающие данные для выбора среди рассмотренных конструкций ячеек сумматоров при разработке многоразрядного сумматора по следующим критериям: мощность, PDP и количество транзисторов. Однако из-за расхождения результатов задержек по двум рабочим выходам ячеек сумматоров С<sub>ОUТ</sub> и S трудно сделать выбор в пользу той или иной конструкции по критерию задержки. Например, анализ результатов моделирования показывает превосходство ячейки СПВ по основной операции сложения. Поэтому далее на рис. 8 и в табл. 3 приводятся результаты моделирования этих же сумматоров при работе в составе четырёхразрядных.

Рис. 8. Результаты моделирования четырёх одноразрядных сумматоров при работе в составе четырёхразрядных:

- а) задержка сигнала сложения в четвёртом разряде S<sub>3</sub>;

- b) задержка формирования сигнала переноса четвёртого разряда C<sub>OUT3</sub>;

- с) сравнение сумматоров ТКРС и ПРПС по задержке сигнала сложения по четырём разрядам  $S_{0-3}$ ;

- d) сравнение двух сумматоров МТКРС и ПРПС по задержке сигнала сложения по четырём разрядам  $S_{0.3}$ ;

- e) сравнение двух сумматоров СПВ и ПРПС по задержке сигнала сложения по четырём разрядам  $S_{0-3}$ .

| Таблица 3. Численные значения результатов моделирования задержки $S_{\rm N}$    |

|---------------------------------------------------------------------------------|

| по операции сложения в каждом разряде для каждого из рассматриваемых сумматоров |

|       | S0 (nS) | S1 (nS) | S2 (nS) | S3 (nS) |

|-------|---------|---------|---------|---------|

| ТКРС  | 13.574  | 20.636  | 27.701  | 34.780  |

| МТКРС | 20.533  | 27.459  | 34.390  | 41.324  |

| СПВ   | 11.798  | 19.398  | 27.005  | 34.608  |

| ПРПС  | 14.521  | 20.817  | 27.124  | 33.437  |

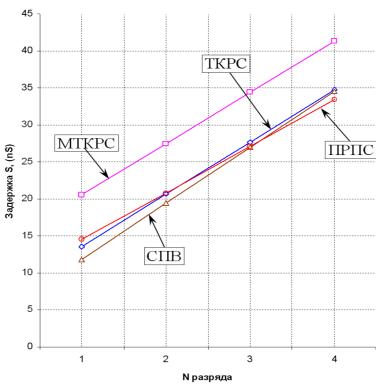

На рис. 9 приводится график зависимости задержки распространения сигнала сложения  $S_N$  от номера разряда для всех четырёх типов ячеек сумматоров, который наиболее наглядно демонстрирует их характеристическое поведение при работе в составе многоразрядного сумматора.

Рис. 9. График зависимости задержки распространения сигнала сложения  $S_{\rm N}$  от номера разряда для всех четырёх типов ячеек сумматоров

## 6. Заключение, выводы

В статье представлена новая схема ячейки полного сумматора на КМОП транзисторах, позволяющая добиться лучшего быстродействия по прохождению сигнала переноса, которое определяет быстродействие многоразрядных сумматоров. Результаты моделирования показывают, что предложенная схема превосходит по быстродействию любой из известных сумматоров при построении сумматоров разрядностью выше трёх. Вследствие линейной зависимости задержки распространения сигнала сложения  $S_N$  от номера разряда это превосходство с ростом разрядности в дальнейшем будет только увеличиваться.

Моделирование одной ячейки сумматора не даёт точной картины о её возможностях при работе в составе многоразрядного сумматора. Поэтому для анализа новых схемотехнических решений ячеек сумматоров требуется моделирование всех известных решений в сумматоре требуемой разрядности либо поиск новых методик сравнения, позволяющих устранить недостаток абстрактного сравнения, приведённого в первой части разд. 5.

# Литература

- 1. *J.M. Rabaey, A. Chandrakasan, B. Nikolic, Digital Integrated Circuits, A Design Perspective*, 2<sup>nd</sup> Prentice Hall, Englewood Cliffs, NJ, 2002.

- 2. J. Uyemura, CMOS Logic Circuit DesigN. Kluwer, 1999, ISBN 0-7923-8452-0.

- 3. N. Weste, K. Eshragian, *Principles of CMOS VLSI Design: A Systems Perspective*, Addison-Wesley, 1993.

- 4. R. Zimmermann, W. Fichtner, "Low-power logic styles: CMOS versus pass-transistor logic", *IEEE J.Solid-State Circuits*, Vol.32, pp.1079-1090, July 1997.

- 5. *A. A. Khatibzaden, K. Raamran,* "A 14-transistor Low-Power High-Speed Full Adder Cell", Department of Electrical and Computer Engineering Ryerson University, Toronto, Ontario, Canada, M5B *2K3*, CCECE 2003 CCGEI 2003, Montreal, May/mai 2003 0-7803-7781-8/03/\$17.00 © 2003 IEEE

- 6. K. Navi, O. Kavehie, M. Rouholamini, A. Sahafi, and S. Mehrabi, "A Novel CMOS Full Adder", 20th International Conference on VLSI Design (VLSID'07), 0-7695-2762-0/07 \$20.00 © 2007 IEEE

- 7. S. Issam, A. Khater, A. Bellaouar, M. I. Elmasry, 1996. "Circuit techniques for CMOS lowpower high performance multipliers", IEEE J. Solid-State Circuit 31, pp. 1535-1544.

- 8. *U. Ko, p.T. Balsara, W. Lee,* "Low-Power Design Techniques for High Performance CMOS Adders", IEEE Transactions on VLSI Systems, Vol. 3, No.2, pp.327–333, June 1995.

- 9. *J.Yuan, C. Svensson*, "High-Speed CMOS Circuit Technique", IEEE JSSC, vol. 24, No.1, February 1989.

- 10. *I. Abu-Khater, A. Bellaouar, M. Elmasry,* "Circuit Techniques for CMOS Low-Power High-Performance Multiplier", IEEE JSSC, vol. 31, No.10, October 1996.

- 11. E. Sicard, S. D. Bendhia, "Basic of CMOS Cell Design", McGraw-Hill, 2007

- 12. *Massimo Alioto, Gaetano Palumbo*, "Analysis and Comparison on Full Adder Block in Submicron Technology", IEEE Trans. On Very Large Scale Integration (VLSI) Systems, Vol. 10, No.6, December 2002, pp. 806–823.

- 13. S. Goel, S. Gollamudi, A. Kumar, M. Bayoumi, "On the design low-energy hybrid CMOS 1-bit full adder cells", in Proc. of the 2004 27<sup>th</sup> Midwest Symposium on Circuits and System, vol. 2, pp. 209–212, July 2004.

- 14. C. H. Chang, J. Gu, M Zhang, "A Review of 0.18-um full adder performances for tree structured arithmetic circuits", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 13, pp.686–695, Issue 6, June 2005.

- 15. В. В. Амосов, "Схемотехника и средства проектирования цифровых устройств", изд. "БХВ-Петербург", 2007.

- 16. Volkan Kursun, Edy G. Friedman, "Multi-voltage CMOS Circuit Design", John Wiley & Sons, Ltd., 2006.

- 17. С. В. Быков, а. с. № 1034031, СССР, G06F 7/50, 07.08.1983.

- 18. *N. Zhuang and H. Wu*, "A new design of the CMOS full adder", IEEE Journal of Solid-State Circuits, vol. 27, No. 5, pp.840–844, May 1992.

- 19. *Шубин В. В.*, Патент на изобретение РФ №2380739, G06F 7/50, Сумматор, ФГУ ФИПС, бюллетень № 3, 27.01.2010.

- 20. *Hubert Kaeslin*, Digital Integrated Circuit Design from VLSI Architectures to CMOS Fabrication. Cambridge University Press, New York, 2008.

- 21. A. Kanuma, "CMOS circuit optimization," Solid-State Electron., vol. 26, no. 1, pp. 47–58, 1983.

- 22. Y.-M. Hsu and E. E. Swartzlander, "Measuring delay time in adders using simulation", in Proc. of the 37th Midwest Symposium on Circuits and System, vol. 1, pp.265–268, Aug. 1994.

- 23. A. M. Shams, T. K. Darwish and M. Bayoumi, "Performance Analysis ofLow-Power 1-Bit CMOS Full Adder Cells", IEEE Trans. on VLSI Systems, Vol. 10, No. 1, February 2002, pp. 20–29.

- 24. В. В. Ракитин, Интегральные схемы на КМОП-транзисторах, МФТИ, Москва, 2007.

- 25. User's Guide. OrCAD PSpice. Oregon: Cadence PCB System Division, 2000.

Статья поступила в редакцию 04.12.2015; переработанный вариант — 21.01.2016.

#### Шубин Владимир Владимирович

к.т.н., начальник Сектора 2 ОКБ АО «НЗПП с ОКБ», доцент кафедры технической электроники СибГУТИ, т. 8-913-903-60-88, e-mail: shubin@nzpp.ru.

#### **CMOS Full-Adder Schematics**

#### Vladimir V. Shubin

In this paper, the base rules of CMOS full-adder cell's circuit technology are described. The most widespread of the constructive solutions in different design styles, their merits and disadvantages are investigated. The results of the simulation and comparison of the described solutions are presented. In addition, a new decision of the CMOS adder cell is proposed. This adder has superior speed characteristics of carry signal shaping while constructing multibit adders.

Keywords: adder, CMOS, circuits design.